Chaos computing

Chaos computing is the idea of using chaotic systems for computation. In particular, chaotic systems can be made to produce all types of logic gates and further allow them to be morphed into each other.

Introduction

Chaotic systems generate large numbers of patterns of behavior and are irregular because they switch between these patterns. They exhibit sensitivity to initial conditions which, in practice, means that chaotic systems can switch between patterns extremely fast.

Modern digital computers perform computations based upon digital logic operations implemented at the lowest level as logic gates. There are essentially seven basic logic functions implemented as logic gates: AND, OR, NOT, NAND, NOR, XOR and XNOR.

A chaotic morphing logic gate consists of a generic nonlinear circuit that exhibits chaotic dynamics producing various patterns. A control mechanism is used to select patterns that correspond to different logic gates. The sensitivity to initial conditions is used to switch between different patterns extremely fast (well under a computer clock cycle).

Chaotic morphing

As an example of how chaotic morphing works, consider a generic chaotic system known as the logistic map. This nonlinear map is very well studied for its chaotic behavior and its functional representation is given by:

- .

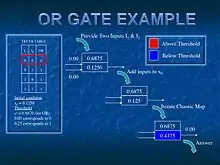

In this case, the value of x is chaotic when r >~ 3.57... and rapidly switches between different patterns in the value of x as one iterates the value of n. A simple threshold controller can control or direct the chaotic map or system to produce one of many patterns. The controller basically sets a threshold on the map such that if the iteration ("chaotic update") of the map takes on a value of x that lies above a given threshold value, x*,then the output corresponds to a 1, otherwise it corresponds to a 0. One can then reverse engineer the chaotic map to establish a lookup table of thresholds that robustly produce any of the logic gate operations.[1][2][3] Since the system is chaotic, we can then switch between various gates ("patterns") exponentially fast.

ChaoGate

The ChaoGate is an implementation of a chaotic morphing logic gate developed by the inventor of the technology William Ditto, along with Sudeshna Sinha and K. Murali.[4][5]

A chaotic computer, made up of a lattice of ChaoGates, has been demonstrated by Chaologix Inc.

Research

Recent research has shown how chaotic computers can be recruited in Fault Tolerant applications, by introduction of dynamic based fault detection methods.[6] Also it has been demonstrated that multidimensional dynamical states available in a single ChaoGate can be exploited to implement parallel chaos computing,[7][8] and as an example, this parallel architecture can lead to constructing an SR like memory element through one ChaoGate.[7] As another example, it has been proved that any logic function can be constructed directly from just one ChaoGate.[9]

Chaos allows order to be found in such diverse systems as the atmosphere, heart beating, fluids, seismology, metallurgy, physiology, or the behavior of a stock market.[10]

See also

References

- Sinha, Sudeshna; Ditto, William (1998). "Dynamics Based Computation". Physical Review Letters. American Physical Society (APS). 81 (10): 2156–2159. doi:10.1103/physrevlett.81.2156. ISSN 0031-9007.

- Sinha, Sudeshna; Ditto, William L. (1999-07-01). "Computing with distributed chaos". Physical Review E. American Physical Society (APS). 60 (1): 363–377. doi:10.1103/physreve.60.363. ISSN 1063-651X.

- Munakata, T.; Sinha, S.; Ditto, W.L. (2002). "Chaos computing: implementation of fundamental logical gates by chaotic elements". IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications. Institute of Electrical and Electronics Engineers (IEEE). 49 (11): 1629–1633. doi:10.1109/tcsi.2002.804551. ISSN 1057-7122.

- Matthew Finnegan (16 Nov 2010). "Scientists use chaos theory to create new chip Chaogate holds exciting processing prospects". TechEYE.net. Archived from the original on 12 May 2014. Retrieved October 15, 2012.

- "Method and apparatus for a chaotic computing module," W. Ditto, S. Sinha and K. Murali, US Patent Number 07096347 (August 22, 2006). U.S. Patent 8,520,191

- Jahed-Motlagh, Mohammad R.; Kia, Behnam; Ditto, William L.; Sinha, Sudeshna (2007). "Fault tolerance and detection in chaotic Computers". International Journal of Bifurcation and Chaos. World Scientific Pub Co Pte Lt. 17 (06): 1955–1968. doi:10.1142/s0218127407018142. ISSN 0218-1274.

- Cafagna, D.; Grassi, G. (2005). Chaos-based computation via chua's circuit: parallel computing with application to the SR flip-flop. International Symposium on Signals, Circuits and Systems. 2. IEEE. p. 749-752. doi:10.1109/isscs.2005.1511349. ISBN 0-7803-9029-6.

- Sinha, Sudeshna; Munakata, Toshinori; Ditto, William L. (2002-02-19). "Parallel computing with extended dynamical systems". Physical Review E. American Physical Society (APS). 65 (3): 036214. doi:10.1103/physreve.65.036214. ISSN 1063-651X.

- Pourshaghaghi, Hamid Reza; Kia, Behnam; Ditto, William; Jahed-Motlagh, Mohammad Reza (2009). "Reconfigurable logic blocks based on a chaotic Chua circuit". Chaos, Solitons & Fractals. Elsevier BV. 41 (1): 233–244. doi:10.1016/j.chaos.2007.11.030. ISSN 0960-0779.

- Soucek, Branko. Dynamic, Genetic, and Chaotic Programming: The Sixth-Generation Computer Technology Series. John Wiley & Sons, Inc. p. 11. ISBN 0-471-55717-X.

- "The 10 Coolest Technologies You’ve Never Heard Of – Chaos Computing," PC Magazine, Vol. 25, No. 13, page p. 66, August 8, 2006.

- "Logic from Chaos," MIT Technology Review, June 15, 2006.

- "Exploiting the controlled responses of chaotic elements to design configurable hardware," W. L. Ditto and S. Sinha, Philosophical Transactions of the Royal Society London A, 364, pp. 2483–2494 (2006) doi:10.1098/rsta.2006.1836.

- "Chaos Computing: ideas and implementations" William L. Ditto, K. Murali and S. Sinha, Philosophical Transactions of the Royal Society London A, (2007) doi:10.1098/rsta.2007.2116.

- "Experimental realization of the fundamental NOR Gate using a chaotic circuit," K. Murali, Sudeshna Sinha and William L. Ditto Phys. Rev. E 68, 016205 (2003). doi:10.1103/PhysRevE.68.016205

- "Implementation of NOR gate by a chaotic Chua’s circuit," K. Murali, Sudeshna Sinha and William L. Ditto, International Journal of Bifurcation and Chaos, Vol. 13, No. 9, pp. 1–4, (2003). doi:10.1142/S0218127403008053

- "Fault tolerance and detection in chaotic Computers" M.R. Jahed-Motlagh, B. Kia, W.L. Ditto and S. Sinha, International Journal of Bifurcation and Chaos 17, 1955-1968(2007)doi:10.1142/S0218127407018142

- "Chaos-based computation via Chua's circuit: parallel computing with application to the SR flip-flop"D. Cafagna, G. Grassi, International Symposium on Signals, Circuits and Systems, ISSCS 2005, Volume: 2, 749-752 (2005) doi:10.1109/ISSCS.2005.1511349

- "Parallel computing with extended dynamical systems" S. Sinha, T. Munakata and W.L. Ditto; Physical Review E, 65 036214 [1-7](2002) doi:10.1103/PhysRevE.65.036214